In a startling revelation that has sent ripples through the cybersecurity community, a group of academic researchers from KU Leuven in Belgium, along with the University of Birmingham and Durham University in the UK, have uncovered a hardware-based attack method that undermines the security of modern processors. Dubbed a low-cost yet highly effective technique, this exploit targets the confidential computing features of leading chip manufacturers, raising serious questions about the safety of sensitive data in cloud environments. With an implementation cost of just $50, the attack highlights a vulnerability that could be exploited with minimal effort, provided there is brief physical access to a system. This discovery challenges the assumption that hardware-level protections are robust enough to withstand insider threats or tampering, prompting a closer examination of how data centers and shared infrastructure can be safeguarded against such innovative exploits.

Unveiling the Hardware Vulnerability

Understanding the Attack Mechanism

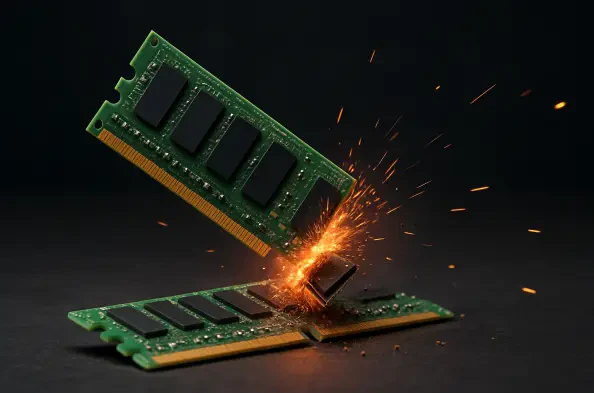

The newly discovered exploit relies on a device known as an interposer, which is strategically placed between the CPU and DRAM memory within a DIMM slot. This setup allows attackers to redirect protected memory addresses to locations under their control, effectively bypassing encryption and boot-time security measures without triggering any alerts in the operating system. Specifically targeting Intel SGX and AMD SEV-SNP—technologies designed to secure sensitive data even from insider threats in cloud setups—this method exposes a critical flaw in memory protection. What makes this approach particularly alarming is its simplicity and affordability, requiring only basic hardware modifications to execute. The attack currently focuses on DDR4 memory systems, though researchers warn that with slight adaptations, such as a more sophisticated interposer, it could potentially extend to DDR5 setups as well, since the underlying issue remains unresolved at the hardware level.

Real-World Implications of Physical Access

While the attack necessitates physical access to the target system, the scenarios in which this could occur are far from theoretical. Rogue employees in cloud service providers, data center technicians with temporary access, or even interference during the manufacturing and shipping of memory modules through supply chain tampering could facilitate such an exploit. Law enforcement actions involving seized hardware also present a plausible risk vector. The ease of execution, requiring only a fleeting interaction with the device, amplifies the concern, as attackers do not need prolonged access to compromise a system. This vulnerability underscores a significant gap in the security model of shared infrastructure, where trust in physical security measures may be misplaced. As data centers increasingly host critical and sensitive information for multiple clients, the potential for such low-barrier attacks to disrupt confidentiality and integrity demands urgent attention from stakeholders across the tech industry.

Industry Response and Future Challenges

Chip Manufacturers’ Stance on the Threat

Upon being notified of this vulnerability earlier this year, both Intel and AMD issued security advisories acknowledging the issue while framing it as outside their primary threat models due to the requirement for physical access. Intel highlighted that its Xeon processors equipped with Total Memory Encryption – Multi-Key (TME-MK) provide additional layers of defense against such hardware-based exploits. However, both companies emphasized that protecting physical access to devices remains a critical responsibility for system owners and operators. This stance has sparked debate, as it shifts some of the burden of security onto end-users and infrastructure providers. While software or firmware updates cannot address this hardware flaw, as confirmed by the researchers, the manufacturers’ responses suggest a reliance on external safeguards rather than intrinsic design changes to mitigate the risk posed by such innovative attack methods.

Addressing the Gap in Hardware Security

The public disclosure of technical details for constructing the interposer by the research team has added a layer of complexity to the issue, balancing the need for transparency with the risk of enabling malicious actors. This decision reflects a broader concern within the cybersecurity field about how to handle the dissemination of exploit information responsibly. Looking ahead, the incident exposed by this research serves as a wake-up call for the industry to prioritize enhanced physical security protocols and explore new hardware architectures that can inherently resist such low-cost tampering. The limitations of scalable memory encryption technologies became evident through this exploit, pushing for a reevaluation of trusted execution environments in protecting data. As threats evolve, collaboration between chip makers, cloud providers, and security experts is deemed essential to develop robust defenses, ensuring that the lessons learned from this vulnerability shape stronger safeguards for the future of computing infrastructure.